The full adder.

This is the first full circuit that will go into our home-brewed processor and is in the Arithmetic and Logic Unit (ALU). It is a mix of the previous circuits explained in previous articles and builds on the half adder circuit in the most recent article.

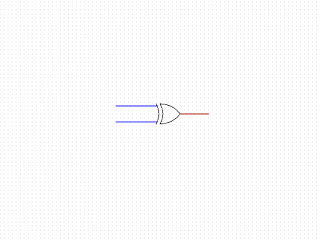

This circuit comprises 2 XOR gates, 2 AND gates and a single OR gate as shown in the diagram below, and adds a single bit. Adding just single bits isn't of much utility on it's own, but this circuit gets repeated with the carry out (c-out) of one connected to the carry in (c-in) of the next up to however many bits are required. Inputs A and B are as you'd expect from previous circuits and the c-in is connected to the previous stage as mentioned.

How it works

I've labelled each of the gates with a number to help with the explanation. You can refer to the truth tables on previous circuits if required as I go through the circuit.

With A, B and c-in all at a logic 0 (FALSE), the circuit outputs 0 on both the SUM and c-out. Even without any explanation of the circuit, this makes sense. We're adding 0 to 0, and whether we're counting in decimal or in binary, the answer is 0.

First, we'll set our inputs as: A = 1, B = 0 and c-in = 0. Gate 1 (XOR) has A at logic 1 and B at logic 0 giving us a logic 1 on it's output which is connected to gate 2 (XOR) and gate 3 (AND). A is also connected to gate 4 (AND). Gate 2 outputs a logic 1 to sum. Gates 3 and 4 both have logic 1 AND logic 0 inputs, so neither outputs a logic 1 to gate 5 (XOR) which means there is a 0 on c-out. Looking at the diagram, we can follow the light green lines for logic 1 and dark green for logic 0. The outputs for this are sum = 1 and c-out = 0.

The second set of inputs we'll put into the circuit are A = 0, B = 1 and c-in = 0. Gate 1 has a single logic 1 input which means it outputs a logic 1 to our sum output, as before. Gate 3 gets the same input as before and outputs a 0. Gate 4 has a single logic 1 (this time on it's other pin) and outputs a 0 as before. Gate 5 gets the same 0,0 input meaning that it outputs a 0 to c-out. The overall result of this is sum = 1 and c-out = 0.

Next, we have a = 1, B = 1 and c-in = 0. Both inputs to gate 1 and logic 1, so this outputs logic 0. As c-in is 0, gate 2 has 2 logic 0 inputs meaning it outputs a 0 to sum. Gate 3 has both inputs 0, so this outputs a 0 to gate 5. Gate 4 has both inputs logic 1, so this outputs logic 1 to gate 5. As gate 5 is an XOR gate, inputs of 0,1 means it outputs a logic 1 to c-out. The overall result is sum = 0 and c-out = 1

Next, we have A = 1, B = 0 and c-in = 1. Gate 1, having a single logic 1 input, gives logic 1 to gate 2. C-in also gives logic 1 to gate 2. Gate 2, having 1,1 inputs gives a logic 0 to sum. The output of gate 1 gives us a logic 1 input to gate 3; the other input of this gate is a logic 1 from c-in. As this is an AND gate, the output is logic 1 to gate 5. Gate 4 has logic 0,1 on it's inputs meaning it outputs logic 0 to gate 5. Gate 5 having logic 1,0 inputs outputs a logic 1 to c-out. The overall result is sum = 0 and c-out = 1.

Inputs of A = 0, B = 1 and c-in = 1 gives us the same outputs as A = 1, B = 0 and c-in = 1 wth the only difference through the circuit being that the inputs on gates 1 and 4 are swapped around

The next case is where A = 0, B = 0 and c-in = 1. Gate 1 has 0,0 as inputs meaning it outputs a logic 0. Gate 2 has a single input at logic 1, so it outputs logic 1 to sum. Gate 3 has only a single logic 1 input, so outputs 0. Gate 4 has 0,0 as inputs, meaning output is 0. This means that gate 5 has logic 0,0 inputs, so gives logic 0 to c-out. The overall result is sum = 1 and c-out = 0

Last of all, we have inputs A = 1, B = 1 and c-in = 1. Gate 1 inputs being 1,1 gives logic 0 output to gate 2. C-in gives logic 1 to gate 2 meaning it's inputs are 0,1 so it outputs logic 1 to sum. Gate 1 gives logic 0 to gate 3 and c-in gives logic 1 to that gate giving 0,1 inputs. This means gate 3 outputs logic 0 to gate 5. A and B being logic 1 means gate 4 inputs are 1,1 giving an output of logic 1 to gate 5. Gate 5 now has inputs 0,1 so it outputs logic 1 to c-out. Overall results are sum = 1 and c-out = 1.

Truth table for the 1-bit full adder circuit:

| A |

B |

c-in |

sum |

c-out |

| 0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

1 |

| 0 |

0 |

1 |

1 |

0 |

| 1 |

1 |

1 |

1 |

1 | | | | |

A 1-bit adder is a great circuit, but it is still only a very basic building block on it's own. It becomes very useful when chained together with other 1-bit adders to create 2, 4, 8, 16 (and more) adders. Modern computers use circuits with "words" as powers of 2; that is 4, 8, 16, 32 (etc), but that wasn't always the case. In the context of computing, a "word" is just how many bits wide data and is. Examples include the PDP-8 which used 12-bit words and was, according to wikipedia, the first commercially successful minicomputer and the pdp-1 pdp-4 pdp7 pdp-9 pdp-15 which all used 18-bit words.

To make the 1 bit adder wider, which only means it works on more bits at a time, we wire the carry-out of the least significant bit to the carry-in of the next most significant, and so on. Think of this in normal maths terms as being the carry from the units column to the tens, the tens column to the hundreds, the hundreds column to the thousands and so on.

The diagram below shows only 3 1-bit adders chained together, but when designing a computer, we can design it to use as many bits wide as we choose. Modern convention is, as mentioned above, to use powers of 2 with most being 64-bits wide nowadays.

In the diagram, the least significant bit of word A goes into the top adder, the next least significant bit goes into the middle one and so on. The same is true for word B. In normal decimal maths terms, the units column goes in the top one, the tens column in the middle and the hundreds in the bottom.

Of note, the computer which is being designed here will use either 8 or 16 bit words; I've not decided, yet, but it will certainly not be 3 bit words :)

Comments

Post a Comment